前面所探究的模数转换器 (ADC)(第 8 部分和第 9 部分)都是基于一个线性内插(闪存)或一个二进制搜索树(管线架构和 SAR 架构)。Δ-Σ 转换器是一款简单的、1 位 ADC,该 ADC 以极高的采样速率(该采样速率可以对一个大采样结果进行平均分配)运行,以获得高精度。

输入信号的数字表现取决于 1 在高速位流中所占的百分比。这是由叫做抽取滤波器的电路来完成的,以确定最终的转换值。

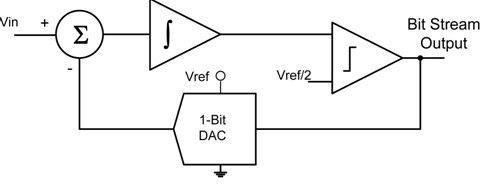

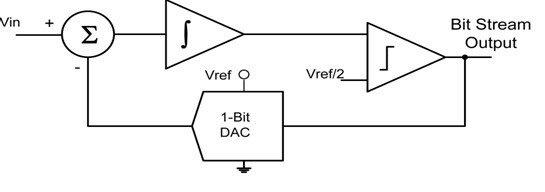

该电路可被称为 Δ-Σ 转换器,也可被称为 Σ-Δ 转换器。但是,人们更接受 Δ-Σ 转换器这个称谓,因为它描述了运行的顺序。该转换器的核心部件为调制器(请参见图 1)。

图 1 Δ-Σ 调制器

前面所述的所有转换器均为开环系统。Δ-Σ 调制器为一个可使输出端数字 1 的平均数量与满量程输入信号的百分比保持一致的闭环系统。在环路为实现平衡而进行不断的搜索时,应考虑到事件发生的序列。

- 在调制器启动时,积分器输出较低,因此比较器将 DAC 输出设置为 Vref,并发送一个 1 至数据流中。请注意,这只是发送至下一个级的第一个位,可能不是最终数据字码的 MSB。

- 施加到积分器的电压为 Vin 和 Vref 之间的差。

- 如果 Vin 值较大,那么施加到积分器的信号就较小。因此,必须在积分器处积累多个采样,以使其输出能够超过比较器阈值。

- 当积分器输出超过比较器开关点时,下一位将变为 0,这会使 DAC 输出一个低电压。

- 这就导致了一个会从积分器中扣除的大电荷。

- 如果 Vin 较小,那么积分器上的第一个电荷将较大。电压 (Vref-Vin) 将会较大,并为一个置于输出位流上的电压。其占用了几个低DAC 输出(位流上相对应的值为0),以此来平衡积分器上大的初始电荷。

- 输出比较器通常被称为1位ADC。

- 对比较器输出进行采样,同时以时钟时间为基础对DAC 进行刷新。

该循环不断进行并使位流中 1 的百分比相当于满量程电压 (Vfs) 的 Vin 百分比。如果 Vin 为 Vfs 的一半,那么位流将包含相等数量的 1 和 0。在其他一些应用中,这种输出流编码被称为脉冲比例调制 (PPM)。

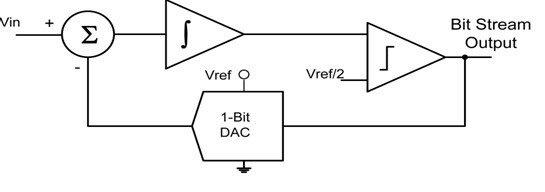

在调制器输出中,理想 PPM 序列偏离是噪声的一种形式。积分器是一种单极、低通滤波器。因此,通过再添加一个积分器的方法(请参见图 2),可以降低噪声水平。

图 2 二阶 Δ-Σ 调制器

由于这是一个闭环系统,因此添加更多的输入积分器会引起稳定性的问题。

上面所描述的一些调制器都伴随有一个数字低通滤波器,以及一个抽取滤波器。这些数字电路建立了输出数据速率,该数据速率与输入信号进行采样的速率大不相同。设计这些滤波器的方法决定了数据延迟。从输入信号一个步阶改变到一个稳定数字输出所需的时间(反映该变化),将始终都至少为一个数据周期。不同的滤波器设计要求具有不同数目的数据周期来达到一个稳定的输出。

这种技术使转换噪声变为高输入采样频带,并远离相关的频带。

Bonnie Baker's Best系列文章

http://tomoson1208.spaces.eepw.com.cn/articles/article/item/85533

http://tomoson1208.spaces.eepw.com.cn/articles/article/item/85592

http://tomoson1208.spaces.eepw.com.cn/articles/article/item/85671

http://tomoson1208.spaces.eepw.com.cn/articles/article/item/85896

http://tomoson1208.spaces.eepw.com.cn/articles/article/item/86075

有关Power的更多的技术文章

http://tanxin0528.spaces.eepw.com.cn/articles/article/item/85530

http://tanxin0528.spaces.eepw.com.cn/articles/article/item/85584

http://tanxin0528.spaces.eepw.com.cn/articles/article/item/85670

http://tanxin0528.spaces.eepw.com.cn/articles/article/item/85895

http://tanxin0528.spaces.eepw.com.cn/articles/article/item/86073