作者:Kevin Duke 德州仪器

文章转自德州仪器在线技术支持社区,原文地址:

http://www.deyisupport.com/blog/b/analogwire/archive/2013/11/06/51562.aspx

今天,我们将介绍两种相关的动态参数 — 压摆率与建立时间。如欲了解更多有关静态和动态参数的不同之处,敬请参阅本文。

什么是压摆率?

TI退休员工模拟专家 Bruce Trump 在《The Signal》上最后发表的一篇博客文章中很好地对压摆率进行了总结,将其描述成运算放大器的速度极限。DAC压摆率参数与运算放大器的压摆率参数成 1:1 关系。

在基本情况下,当输入电压发生明显变化时(例如当新的 DAC 代码被锁存在距离当前代码有几个代码的位置),这时输出放大器将开始摆动,即以最快的速度增大输出电压。输出放大器保持这种状态直到接近预期值为止,同时输出开始在指定的误差频带范围内趋于稳定。

产品说明书规范介绍了 DAC 出现摆动时在其输出端可以看到的最大变化率,通常是每秒几微伏。

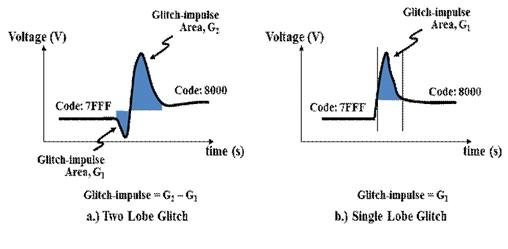

注意:该图并非根据真实器件按比例绘制,而是经放大后显示的各个区域

什么是建立时间?

DAC 的建立时间与运算放大器建立时间有着惊人的相似之处。另外,主要的区别在于 DAC 建立时间还包含停滞时间分量。停滞时间是 DAC 锁存或更新输出所用的时间。锁存行为通常由数字信号的下降沿(称为 LDAC)触发。LDAC 与 DAC 输出的交互情况如下图所示,该图摘自 DAC8568 说明书。

如果出现非常大的输入步进,DAC 将进入摆动区域,这在上面的两幅图中均有显示。在摆动区域内,DAC 的前进会受到压摆率参数的限制。如果 DAC 确实需要摆动,那么建立时间的下一个阶段将处于过载恢复状态,紧接着是达到指定误差频带所需的线性建立时间。对于 DAC 来说,误差频带通常指定在 1LSB 以内。

产品说明书中针对较大步长给出了建立时间参数。例如,DAC8568 的指定建立时间为 5us,通常针对的范围是从 ¼ 满量程输出到 ¾ 满量程输出。

切记,摆动时间占总体建立时间的绝大部分,因而如果您的输出步长小于说明书中规定的建立时间规范,那么系统建立所用的时间就会变短。在大部分高精度应用中,建立时间是 DAC 的有效更新速率。

本文将对《模拟线路》上的DAC 基础知识做一个终结。此外,别忘了观看我同事 Rahul Prakash 主讲的最新“设计精萃”视频 — 关于乘法 DAC (MDAC)。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。