作者:Michael Peffers 德州仪器

在本文中,我们将探讨差分信号的优势以及这些优势如何对您的高速设计产生积极影响。

TTL、CMOS 以及其更低电压的同类 LVTTL 与 LVCMOS 等单端信号都是数字电路设计中的常用技术。然而,使用这些类型的信号发送技术有一些不足,其最终会限制高速设计。由于不同接地电势和高压摆率,单端信号在远距离通信时运行非常吃力。针对每个信号在正负电轨间切换的单端驱动器需要一个高 ΔV/Δt,这就意味着您需要各种负载的电流 (I = CΔV/Δt)。因此,轨至轨信号(大 ΔV)的局限性就显而易见了:需要更多的电源来实现更短的转换时间(更小的 Δt)。那么我们应如何围绕数字设计获得高速信号,并避免单端信号的损耗呢?实施差分信号!

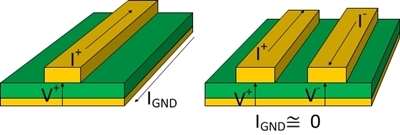

图 1:单端信号拓扑(左)/差分信号拓扑(右)

差分系统一般是三导线系统(也可能更多),包含非反相信号、反相信号以及接地参考。在理想情况的差分系统中,V+ = -V- 和 |I+| = |I-| 可产生平衡的信号。在平衡差分拓扑中,两根导线紧密耦合在一起,净接地电流 (IGND) 等于零。在系统中实施差分信号拓扑有各种优势,包括更高的信号发送速率、高共模噪声抗扰度以及更低的功耗等。

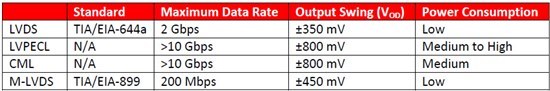

采用差分信号,升降时间大体会比单端信号短,因此在当前通信系统中 10 Gbps 以上数据速率已成为一个可实现的标准。更小的信号摆幅可使系统整体功率预算降低。LVPECL 和 CML 差分信号具有更高的输出电压摆幅,因此功耗比 LVDS 及 M-LVDS 信号略高。

差分信号传输的第二个优势在于共模噪声抗扰度。由于差分信号由幅值相等、极性相反的正负信号组成,因此耦合到传输信号上的任何共模噪声都会被其询问所抵消。这绝对是巨大的系统优势,因为很可能会有一些开关稳压器连接至电源及接地面板,其只是在等待将其能量耦合到您清洁的信号上。这可能开始觉得不算什么,但您很快会发现当严格的抖动预算对设计至关重要时,每微微秒都非常关键!

下表是最常见差分信号拓扑的摘要,其因功耗、性能及应用领域的不同而不同:

一个优异的差分信号应用实例是将单端 VCO 输出连接至需要差分 LVDS 时钟输入的 FPGA 或串行解串器。为避免因满足这一需求而破坏原本已非常稳定的系统时钟架构,您可实施一款器件(如 SN65LVDS1 单路 VDS 发送器等)来执行 VCO 与终端器件之间的单端至差分信号转换。SN65LVDS1 采用 2.4V 或更高电源电压运行,理想适用于没有 3.3V 电轨的低功耗应用。

原文请参见: http://e2e.ti.com/blogs_/b/analogwire/archive/2014/02/21/get-connected-differential-signaling.aspx

如需更多产品信息,请点击链接:

SN65LVDS1

www.ti.com.cn/hpa-int-cif-sn65lvds1-china020-contrib-pf-cn

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。